Problématique : Un simple récepteur SPDIF "classique" ne suffit pas. Sur une carte de traitement DSP, la fréquence de "traitement" des échantillons est en général fixée à la conception et dans tous les cas au moment de la définitions des paramètres et coefficients des traitement logiciels qui vont être appliqués aux échantillons.

Beaucoup d'unités de traitement DSP n'ont même pas d'entrées numérique et embarquent sous une forme ou une autre (intégré au DSP ou externes) leur convertisseurs Analogiques/Numériques. La fréquence d’échantillonnage est donc fixée en interne selon les choix des concepteurs.

D'autres ont des entrées numériques, mais intègrent également sous une forme ou une autre (toujours intégré au DSP ou externe) ce que l'on appelle un ASRC pour Asynchronous Sample Rate Converter. Le rôle d'un ASRC est de réaliser une conversion de fréquence d'échantillonnage par décimation ou interpolation et ce de manière asynchrone à l'horloge des échantillon en entrée.

L'utilisation d'un ASRC va donc permettre de convertir la fréquence des signaux numériques en entrée à celle choisie par conception pour l'ensemble des traitements DSP (sample rate converter). Il va permettre également à la plateforme de traitement de rythmer la fourniture des échantillons selon sa propre horloge sans que celle ci n'ait une corrélation quelconque avec celle du signal en entrée (asynchronous).

Dans le cas du DSPiy, la fréquence de base de traitement a été fixée à 96khz (paramétrable également à 48khz en changeant et recalculant tous les traitement "mathématiques"). En plus des deux entrée analogiques, nous avons une entrée numériques I2S maitre pour les signaux numériques. Ce DSP d'entrée de gamme n'intègre pas d'ASRC.

la D-IN V1 : Afin de répondre à un besoin réel et légitime d'entrée numériques pour le DSPiy et néanmoins partager le travail et ne pas complexifier à outrance la carte de base, je me suis proposé pour réaliser un add-on au DSPiy autour du circuit de Cirrus Logic CS8422 intégrant un récepteur SPDIF et un ASRC.

Le CS8422 est dans la gamme ce de qui se fait de mieux, reste simple à mettre en œuvre et est a prix contenu.

Son concurrent chez TI est certes plus performant et beaucoup plus complet (deux port I2S bidirectionnels, deux ASRC, récepteur et émetteur spdif), mais pour deux fois plus cher, avec 12 broches de plus, et nécessite obligatoirement d'être programmé par un µ-controleur.

On part petit et au final ....

- une entrée coaxiale sur transfo et une entrée optique supportant jusqu'à 211khz sélectionnable (2 entrées indépendantes).

- Haute Tolérance au Jitter en entrée et Ultra-Low Jitter Clock Recovery

- un ASRC supportant jusqu'à 216khz (entrée I2S), et un ratio de 6:1 à 1:6, 140dB de dynamique et -120dB de THD+N

- une sortie spdif pass-through sur transfo pour coax et sur TOSLINK sur extension pcb sécable (si on en a pas besoin). Le choix de l'entrée sélectionée pour le pass-through est indépendant du choix de l'entrée utilisée par le CS pour les autres traitement, en faisant un véritable mini switch spdif indépendant.

- utilisable en mode soft (i2c) ou en mode hard à base de jumpers.

- peux fonctionner sans clock, emplacement pour clock HTCMOS format 7x5 pour perf maximales de l'asrc en mode Soft ou master-clock locale en mode hard.

- s'intègre par simple empilement sur le DSPiy

- deux sorties PCM/I2S/TDM master ou slave

- en mode soft, une entrée PCM/I2S , master ou slave, isolée ou non, pour par exemple interface USB -> I2S

- led de "lock" sur entrée spdif

- reporting des erreurs et détection de signal spdif, détection de présence de signal audio dans le flux spdif

- décodage des info additionnelles User spdif accessible en i2C ou en mode hard.

- 98% des fonctionnalités du CS8422 sont au final exposées sur la carte

- double régulation intégrée à base d'adp151, régulateurs très faibles bruits 3.3V. Alimentation de la carte en 5V max.

- utilisation de GPO pour la sécurisation des isolateurs en mode soft

- utilisation de GPO1 comme ligne d'interruption en mode soft

- nombreuses possibilités de génération ou de réception de master clock

- extension double oscillateur pour pouvoir utiliser des SOCs sous Linux par exemple en I2S ou TDM slave pour s'affranchir de tous les problèmes d’approximations d'horloge I2S sur ces chips. (utilisations de deux oscillateurs Silicon Labs Si510)

Au niveau construction :

- tout a été fait pour que l'assemblage de la carte soit possible en DIY malgré sa conception 100% CMS.

- à l'exception de 4 ferrites en 0805, tous les composants sont en 1206

- l'entrée et la sortie coax peuvent se faire sur RCA ou sur BNC suivant l'embase choisie (voir BOM)

- en mode soft, l'ensemble des composants nécessaire à son fonctionnement sont sur le dessus à l'exception d'une résistance et d'un condensateur. Quelques composants supplémentaires sont à souder sur l'autre face si on a besoin de l'entrée I2S isolée en mode master (cas peu courant).

- seul un ensemble de résistance est à souder face AR pour avoir accès à l'ensemble des fonctionnalités en mode hard en jouant sur des jumpers

-tous les jumpers sont des jumpers "cms à souder" : un point de soudure à poser ou enlever.

- même les configurations les plus exotiques sont accessibles en mode hard en changeant la valeur de certaines résistances par rapport à la BOM de base (voir doc, chapitre : configuration très avancée)

- les connecteurs proposés permettent un empilement de 6mm avec le DSPiy permettant l'utilisation d'entretoises courantes. (TLW +SLW samtec)

- la carte peut être réalisée aussi bien en 1.5mm qu'en 1mm pour avoir une hauteur d'empilement totale de 7mm ou 7.5mm toujours pour utiliser des tailles d'entretoise courantes.

- tous les points de connexions sont alignés sur une grille de 2.54 ou de 1.27 à quelques pouillèmes près pour pouvoir facilement s'intégrer à un autre projet, le placement du connecteur d'alim, de la sortie I2S principale et du bus i2c + GPO1 ayant eux été dictés par leur position sur le DSPiy, comme les 4 trous de fixation.

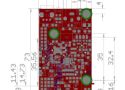

- la carte fait 40mm x 73mm, l'extension faisant 45mm x 18mm pour un hors tout total de 85mm x 73mm

- la version sans extension fait 40mm x 73mm

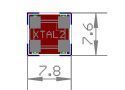

- l'option XTal2 est sur un petit PCB a part de 7.6mm x 7.8mm

Bref, cette carte a été conçue à la base pour le DSPiy mais est faite pour être utilisable / utilisée dans tout projet ayant besoin de SPDIF et ou d'ASRC, sans exclure les cas tordu, aussi bien en hard que piloté par I2C pour un prix serré (prix estimatif à évaluer précisément une fois le proto monté).

En attendant la doc détaillée de configuration, se reporter à la datasheet sur le site du constructeur et au schéma ci dessous.

L'archive de la version finale V1.6.

Elle contiens toute les variantes: f (full), n (no pass-through), r (pass-through RCA), t (pass-through Toslink), d (DSPiy : pt RCA + connecteur plug&play amanero).

Schéma et tous les gerbers. J'ai pas eu le courage de re-générer des PDF d'illustration ou les screenshots.

Les contraintes de fabrication : piste min 0.2mm, interpiste min 0.15mm, via min 0.3mm. Ça passe chez Printed.

Historique:

La V1.2 est la version proto corrigée

La V1.3 a amené la version avec connecteur Amanero + quelques corrections de routage : C'est la version de prod de la CG1.

La V1.4 a amené d'autres corrections mineures et l'ajout d'un meander sur la ligne LRCK.

La V1.5 corrige le placement d'une piste qui dégradait le plan de masse autour du CS.

La V1.6 corrige le bug différentiel/asymétrique (C33 et C34) et rajout de C35 pour découpler le primaire du transfo de sortie spdif.

la D-IN-DSPIY-V1R0 : Thierry a sorti une DPSIY-V1 sur la base du schéma de la V1 épuré du mode hardware et de tout le superflu non nécessaire au DSPiy afin de réduire les couts de production et simplifier la fabrication.

la D-IN V2 : Je prendrai peut être la décision de re-router la V1 en tenant compte des leçons apprises. Je changerai également peut être le format de la carte, la D-IN-DSPIY-V1 étant plus adapté pour le DSPiy.

Très beau schéma, voilà une future carte multi usage via les configs.

Très beau schéma, voilà une future carte multi usage via les configs.